# Harvesting Circuits for Miniaturized Photovoltaic Cells

Rajiv Damodaran Prabha, Gabriel A. Rincón-Mora, and Suhwan Kim Georgia Tech Analog, Power, and Energy IC Research {rajiv.damodaran, rincon-mora, suhwan}@gatech.edu

Abstract-Miniaturized systems like wireless microsensors suffer from short operational lifetimes because they lack space to store the energy that wireless transmission, signal conditioning, and monitoring require to operate across time. Harvesting ambient energy circumvents this limitation because the environment is a virtually boundless reservoir of energy. Of available sources, solar light produces the highest power density, and although artificial lighting is not as rich, thermal and magnetic sources produce even lower power densities and mechanical and chemical transducers are difficult to integrate. The problem is microscale photovoltaic (PV) cells only produce 1 and 100  $\mu$ W/mm<sup>2</sup> for artificial and solar lighting, so the act of conditioning and transferring power can dissipate most, if not all, of the power available. The focus of this paper is to introduce and discuss the design challenges associated with harvesting circuits when harnessing, conditioning, and transferring power from tiny PV cells that only generate  $1 - 100 \mu$ W.

## I. HARVESTING MICROSYSTEMS

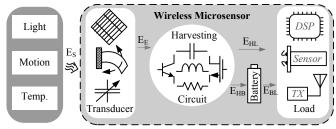

Although recent advances in the semiconductor industry suggest that integrating sensors, processors, memory, and radio transceivers into a wireless microsensor node is possible [1]–[2], powering these devices across extended periods remains an issue. The problem is limited space, because small batteries store little energy and replacing or recharging them periodically presents prohibitive personnel costs. Fortunately, because power-hungry functions like telemetry (TX in Fig. 1) seldom engage in a sensor node, drawing energy from the environment to continually charge a small battery is a viable and appealing alternative [1], [3].

Fig. 1. Harvester-powered wireless microsensor.

Of available ambient sources, solar light offers the highest power density at more than 15 mW/cm<sup>2</sup> [4]. Artificial lighting generates considerably lower power at 10 – 100  $\mu$ W/cm<sup>2</sup>, but thermal and magnetic sources produce even less at 1 – 15  $\mu$ W/cm<sup>3</sup>. The challenge with piezoelectric and chemical transducers is integration. Kinetic energy in motion may produce moderate power at 1 – 300  $\mu$ W/cm<sup>3</sup>, but not all applications vibrate. Ultimately, because solar energy generates so much power, as Table I shows, light remains an alluring source for many practical applications. Still, harnessing light energy from tiny photovoltaic (PV) cells constrains power to below 100  $\mu$ W/mm<sup>2</sup>, which parasitic components in the cell and the harvester circuit can exhaust.

| Sources                            |            | Transduction    | Estimated Power         |

|------------------------------------|------------|-----------------|-------------------------|

|                                    |            | Mechanism       | Density                 |

| Light                              | Solar      | Photovoltaic    | $< 15 \text{ mW/cm}^2$  |

| Light                              | Artificial | (PV)            | $10 - 100 \ \mu W/cm^2$ |

| Motion                             |            | Electrostatic   | $50 - 100 \ \mu W/cm^3$ |

|                                    |            | Electromagnetic | $< 1 \ \mu W/cm^3$      |

|                                    |            | Piezoelectric   | $50 - 300 \mu W/cm^3$   |

| $\Delta$ Temp. (10 <sup>o</sup> C) |            | Seebeck         | $5 - 15 \mu W/cm^3$     |

TABLE I. POWER DENSITIES FROM AMBIENT ENERGY SOURCES.

The aim of this paper is to introduce and discuss the challenges involved in harnessing light energy from miniaturized PV cells that generate less than 100  $\mu$ W. To that end, Section II describes the electrical characteristics of PV cells that dictate (in Section III) the operating boundaries of a harvesting microsystem. Section IV then discusses and compares the design and efficiency performance of two basic harvesting approaches: switched-inductor and switched-capacitor circuits and Section V draws relevant conclusions.

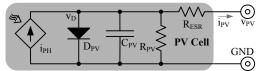

### II. MINIATURIZED PHOTOVOLTAIC CELLS

Photons in incident light strike and break apart electron-hole (E-H) pairs in photovoltaic (PV) cells to generate current  $i_{PH}$ . Because PV cells are, at their core, pn-junction diodes,  $D_{PV}$  in the model of Fig. 2 [7] shunts and forward-biases with  $i_{PH}$ , if not steered elsewhere.  $D_{PV}$ 's junction capacitance  $C_{PV}$  also shunts  $i_{PH}$ , as does the parasitic peripheral shunt resistance across the structure  $R_{PV}$ . In conducting the fraction of  $i_{PH}$  that flows out of the cell as  $i_{PV}$ , equivalent series (contact) resistances (ESR)  $R_{ESR}$  raise  $D_{PV}$ 's voltage  $v_D$  to boost  $D_{PV}$ 's shunting effect on  $i_{PH}$ .  $R_{PV}$  and  $R_{ESR}$ 's combined impact on  $i_{PV}$ , however, is normally negligible in these tiny devices because  $R_{ESR}$  is small at a few  $\Omega$ 's and  $R_{PV}$  large at M $\Omega$ 's:

$$i_{PV} = i_{PH} - I_{S} exp\left(\frac{v_{PV} + i_{PV}R_{ESR}}{V_{t}}\right) - \left(\frac{v_{PV} + i_{PV}R_{ESR}}{R_{PV}} || \frac{1}{sC_{PV}}\right)$$

$$\approx i_{\rm PH} - I_{\rm S} \exp\left(\frac{v_{\rm PV}}{V_{\rm t}}\right) - sC_{\rm PV}v_{\rm PV}, \qquad (1)$$

where  $V_t$  is the thermal voltage and  $C_{PV}$  depends on  $v_{PV}$ .

Fig. 2. Photovoltaic (PV) cell model.

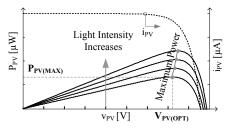

Given a particular light intensity and corresponding  $i_{PH}$ ,  $D_{PV}$ 's shunting current  $i_D$  increases with  $v_{PV}$ . Accordingly, output power  $P_{PV}$ , or  $i_{PV}v_{PV}$ , grows with  $v_{PV}$  as long as the rise in  $P_{PV}$  exceeds that of diode power  $P_D$ , which is why  $P_{PV}$ peaks (at  $P_{PV(MAX)}$  in Fig. 3) when  $\Delta P_D$  begins to exceed  $\Delta P_{PV}$ (at optimum diode voltage  $V_{PV(OPT)}$ ). Increasing light intensity raises  $i_{PH}$  (and  $P_{PV}$ ), so  $i_D$  (and its corresponding  $V_{PV(OPT)}$ ) can rise before offsetting  $\Delta P_{PV}$ . Therefore, tracking maximum power-point  $V_{PV(OPT)}$  with respect to light intensity ensures the PV cell generates  $P_{PV(MAX)}$ .

Fig. 3. Typical photovoltaic (PV) cell's power-current-voltage (P-I-V) curves.

#### **III. HARVESTING EFFICIENCY**

The acts of converting, transferring, and conditioning energy dissipate power, which is why a harvesting system ultimately supplies a fraction of the energy it receives. A PV cell, for example, converts a fraction of photon source energy  $E_S$  (from Fig. 1) into the electrical domain  $E_E$  as  $i_{PH}$ . Then, depending on how well the system tracks  $V_{PV(OPT)}$ ,  $D_{PV}$ ,  $R_{PV}$ , and  $R_{ESR}$  in the cell dissipate a fraction of  $E_E$  to output  $E_{PV}$  in  $i_{PV}$ . The harvesting circuit, which transfers and conditions  $E_{PV}$  to charge a battery and supply a load, also consumes power, reducing  $E_{PV}$  to usable harvested energy  $E_H$  (i.e.,  $E_{HB}$  and  $E_{HL}$  in Fig. 1). As a result, the system efficiency of the harvester ( $\eta_S$ ) is the product of photon- $i_{PH}$ ,  $i_{PH}$ - $i_{PV}$ , and conversion efficiencies  $E_E/E_S$  or  $\eta_{PH}$ ,  $E_{PV}/E_E$  or  $\eta_{PV}$ , and  $E_H/E_{PV}$  or  $\eta_{CONV}$ :

$$\eta_{\rm S} = \eta_{\rm PH} \eta_{\rm PV} \eta_{\rm CONV}. \tag{2}$$

# A. Light-Current Conversion

Of the photons available in incoming light, only those with energies exceeding the band-gap energy of the semiconductor used to build the PV cell can break apart E-H pairs to generate  $i_{PH}$ ; the material loses excess photon energy as heat. Lightconversion efficiency  $\eta_{PH}$  is therefore highest when the spectral energy of the incident light peaks at the band-gap energy of the material. Given this, when exposed to solar light, crystalline silicon outperforms other low-cost semiconductor technologies with efficiencies of 15% to 20% [5]. Amorphous silicon is slightly better under artificial lights and 10% to 20% cheaper, but the absence of a dedicated process and the conversion efficiency of its crystalline counterpart (under variable lighting conditions and limited area) outweigh this small positive offset.

## B. Tracking Performance

The act of tracking  $V_{PV(OPT)}$  also consumes energy, so balancing tracking accuracy with processing power is important. Predicting (rather than measuring)  $V_{PV(OPT)}$ 's optimum open-circuit point from empirical information typically offers the best tradeoff [6]–[7], because processing power is low. Monitoring the cell's open-circuit voltage is a weakness, however, because sensing a small open-circuit replica of the cell is wasteful of silicon area (i.e., cost) just as disconnecting the cell is of power (i.e., efficiency).

#### **IV. HARVESTER CIRCUIT**

The application space this research targets is light-powered chip-sized sensors that operate continuously, even under cloud cover and artificial lights. Accordingly, this section describes the design constraints such an application places on a harvester circuit. Since the fundamental aim of the system is to generate output power, understanding where and how these circuits dissipate energy is vital, which is why, after operation and design, the focus here shifts to efficiency.

## A. System Requirements

Tiny 2  $\times$  2-mm<sup>2</sup> PV cells typically generate less than 100  $\mu$ W, even under direct sunlight. C<sub>PV</sub> for these devices is roughly 1 nF and, since  $D_{PV}$ 's current increases exponentially with  $v_{PV}$ ,  $V_{PV(OPT)}$  falls slightly below 0.6 - 0.7 V to around 0.55 V. Therefore, to charge a super capacitor at 1 V (i.e.,  $V_0$ ), for example, the harvester circuit must boost the cell's 0.55 V to 1 V with a switched-inductor (SI) or -capacitor (SC) circuit (because unswitched circuits cannot boost voltages). The switching action, unfortunately, produces a ripple at  $v_{PV}$  that deviates it from  $V_{PV(OPT)}$ , so variation  $\Delta v_{PV}$  must remain small (e.g., 50 mV) for  $P_{PV}$  to stay near  $P_{PV(MAX)}.$  Regulating  $v_{PV}$ about  $V_{PV(OPT)}$ , whether it be an SI or SC circuit, requires a feedback controller that must, by design, operate in subthreshold (with nA's) to consume a diminutive fraction of P<sub>PV</sub>. In all, SI and SC implementations must condition the PV cell according to these requirements, which Table II summarizes.

TABLE II. SYSTEM REQUIREMENTS

| Parameter       | Value                  | Design Target        | Value                |

|-----------------|------------------------|----------------------|----------------------|

| P <sub>PV</sub> | $\leq 100 \ \mu W$     | V <sub>PV(OPT)</sub> | 0.55 V               |

| $C_{PV}$        | $\approx 1 \text{ nF}$ | Vo                   | 1 V                  |

|                 |                        | $\Delta v_{PV}$      | $\leq 50 \text{ mV}$ |

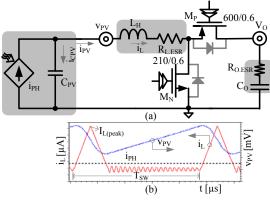

## B. Switched-Inductor (SI) Boost Converter

<u>Operation</u>: SI circuits transfer energy by energizing (closing switch  $M_N$  in Fig. 4a) and de-energizing (closing  $M_P$ ) an inductor  $L_H$  from an input source  $i_{PV}$  into an output  $C_O$  in alternate switching cycles. When  $P_{PV}$  rises,  $L_H$  transfers energy packets more often, so switching frequency  $f_{SW}$  increases. While  $L_H$ 's ESR  $R_{LESR}$ ,  $M_N$ , and  $M_P$  dissipate Ohmic power,  $M_N$  and  $M_P$ 's drivers consume energy to charge and discharge  $M_N$  and  $M_P$ 's parasitic gate capacitances. However, because  $i_{PV}$ is low and transferring small packets of energy requires a high  $f_{SW}$ , Ohmic losses are not as significant as gate-drive losses. Fortunately, operating  $L_H$  discontinuously, which is to say  $L_H$ 's current  $i_L$  rises and falls back to zero in a fraction of the switching period  $T_{SW}$ , as Fig. 4b shows, decreases the number of switching events (i.e., energy losses) per period.

Fig. 4 (a) Switched-inductor circuit and (b) its simulated waveforms.

Design: To keep conduction losses (i.e.,  $\Delta i_L$ ) and system-inpackage (SiP) dimensions low, a 220-μH, 2 × 2 × 1-mm<sup>3</sup> inductor implements L<sub>H</sub>. With this L<sub>H</sub>, M<sub>N</sub> and M<sub>P</sub>'s respective aspect ratios should (at 210μm/0.6μm and 600μm/0.6μm) balance conduction, switching, and control losses to minimize their net sum. Since  $i_L$  is discontinuous and  $i_{PH}$  is, for all practical purposes constant through T<sub>SW</sub>, current difference  $i_L$ –  $i_{PH}$  discharges and charges C<sub>PV</sub>, producing ripple  $\Delta v_{PV}$ . However, because L<sub>H</sub> must energize to and de-energize from  $i_{L(PEAK)}$  (through conduction time t<sub>C</sub>) to store and transfer  $i_{PH}$ 's maximum energy as charge q<sub>L</sub>, worst-case ripple  $\Delta v_{PV(MAX)}$ occurs when  $i_{PH}$  is so small that C<sub>PV</sub> supplies all of q<sub>L</sub>:

$$\Delta v_{PV(MAX)} = \frac{q_L}{C_{PV}} = \frac{0.5 t_C i_{L(PEAK)}}{C_{PV}} \le 50 \text{ mV}, \quad (3)$$

where  $V_{PV(OPT)}$ ,  $V_O$ , and the converter's minimum delay across the loop set  $t_C$  and  $P_{PV(MAX)}$  and  $L_H$  set  $i_{L(PEAK)}$  [10].

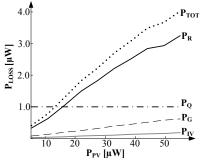

<u>Losses</u>:  $L_H$ 's  $R_{L,ESR}$  and  $M_P$  and  $M_N$ 's combined resistance  $R_{SW,EQ}$  conduct  $i_L$ , so they dissipate root-mean-square (RMS) Ohmic loss  $P_R$ :

$$P_{\rm R} = i_{\rm L(RMS)}^{2} \left( R_{\rm LESR} + R_{\rm SW.EQ} \right).$$

(4)

$M_N$  also consumes power  $P_{IV}$  while conducting  $i_{L(PEAK)}$  and transitioning from zero to  $V_O + V_D$  across overlap time  $t_{OV}$ :

$$P_{\rm IV} = \left[\frac{i_{\rm L(PEAK)}(V_{\rm O} + V_{\rm D})}{2}\right] \left(\frac{t_{\rm OV}}{T_{\rm SW}}\right),\tag{5}$$

where  $V_D$  is  $M_P$ 's body's diode voltage. Plus,  $M_N$  and  $M_P$ 's drivers dissipate energy every cycle to charge and discharge  $M_N$  and  $M_P$ 's combined gate capacitance  $C_{G.EQ}$  across  $V_O$ :

$$P_{\rm G} = \frac{C_{\rm G.EQ} V_{\rm O}^{2}}{T_{\rm SW}} = C_{\rm G.EQ} V_{\rm O}^{2} f_{\rm SW} \,. \tag{6}$$

Because  $L_H$  transfer pockets of energy more often when  $P_{PV}$  increases,  $i_{L(RMS)}$  increases with  $f_{SW}$ , as do  $P_{IV}$  and  $P_G$ , although not to the same extent, as Fig. 5 shows, assuming feedback controller losses  $P_O$  is constant at 1  $\mu$ W.

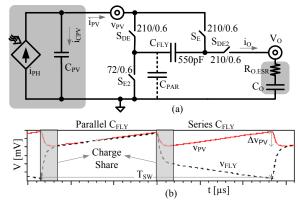

## C. Boosting Switched-Capacitor (SC) Charge Pump

<u>Design</u>: SC circuits boost and transfer energy by first paralleling (i.e., charging) flying capacitors ( $C_{FLY}$  in Fig. 6a) and then connecting (and discharging) them in series with the

source (v<sub>PV</sub>) to output V<sub>0</sub>. In the parallel phase, v<sub>PV</sub> first drops to V<sub>PV(MIN)</sub> because C<sub>PV</sub> de-energizes quickly into partially discharged C<sub>FLY</sub>, as Fig. 6b shows, and then rises to V<sub>PV(MAX)</sub> as i<sub>PH</sub> charges C<sub>PV</sub> and C<sub>FLY</sub> through the phase. In the series phase, v<sub>PV</sub> again drops to V<sub>PV(MIN)</sub> because C<sub>PV</sub> and C<sub>FLY</sub> discharge into C<sub>0</sub> and then rises because i<sub>PH</sub> charges C<sub>PV</sub> and C<sub>0</sub> and discharges C<sub>FLY</sub>. As before, the circuit transfers energy packets more often (i.e., f<sub>SW</sub> increases) when i<sub>PH</sub> rises.

Fig. 5. Simulated switched-Inductor losses across  $P_{PV}$ .

Fig. 6. (a) Switched-capacitor circuit and (b) its simulated waveforms.

<u>Design</u>: Worst-case ripple  $\Delta v_{PV(MAX)}$  occurs when  $i_{PV}$  is low, when only  $C_{PV}$ 's energy charges  $C_{FLY}$  quickly from  $V_{FLY(MIN)}$ to  $V_{PV(MIN)}$  in the parallel phase:

$$C_{PV}\Delta v_{PV(MAX)} = C_{FLY} \left( V_{PV(MIN)} - V_{FLY(MIN)} \right),$$

(7)

and rises slowly from there to  $V_{PV(MAX)}$ . Because  $V_O$  drops across  $C_{PV}$  and  $C_{FLY}$  (with a low  $i_{PH}$ ) at the end of the series phase,  $V_{FLY(MIN)}$  is  $V_O - V_{PV(MAX)}$  and  $\Delta v_{PV(MAX)}$  is

$$\Delta v_{PV(MAX)} \approx \left(\frac{C_{FLY}}{C_{PV}}\right) \left(V_{PV(MIN)} + V_{PV(MAX)} - V_{O}\right)$$

$$\approx \left(\frac{C_{FLY}}{C_{PV}}\right) \left(2V_{PV} - V_{O}\right) \le 50 \,\mathrm{mV}$$

(8)

So, to ensure  $C_{PV}$  does not discharge beyond  $\Delta v_{PV(MAX)}$ ,  $C_{PV}$  (at 1 nF) should be considerably higher than  $C_{FLY}$ . A smaller  $C_{FLY}$ , however, decreases the charge the circuit delivers per cycle, so  $f_{SW}$  and associated losses rise as a result. In this case, switching 550 pF at 74 kHz keeps  $\Delta v_{PV}$  below 50 mV and transistors' aspect ratios in Fig. 6a ensure  $C_{FLY}$  charges completely in the parallel phase (across  $0.5T_{SW}$ ) for the highest possible  $i_{PH}$ .

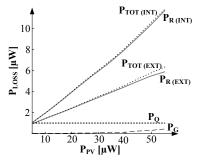

<u>Losses</u>:  $C_0$  charges only in the series phase, and since  $C_{PV}$  does not supply power because there is no net change in its

voltage (i.e., charge) across this phase, only  $i_{PH}$  reaches  $V_O$  (for  $0.5T_{SW}$ ) to deliver  $0.5i_{PH}V_O$  as output power  $P_O$ . Therefore, of  $P_{PV}$  (or  $i_{PH}V_{PV}$ ), the switches dissipate (as Ohmic power  $P_R$ ) what  $C_O$  fails to receive in  $P_O$ :

$$P_{\rm R} = P_{\rm PV} - P_{\rm O} = i_{\rm PH} (V_{\rm PV} - 0.5 V_{\rm O}), \qquad (9)$$

so, irrespective of the resistance (size) of the switch,  $P_R$  increases with  $i_{PH}$ , as does  $f_{SW}$ . An on-chip  $C_{FLY}$ , unfortunately, introduces a parasitic bottom-plate capacitor  $C_{PAR}$  (at roughly  $0.1C_{FLY}$  [8]) that an off-chip  $C_{FLY}$  does not, so the switches dissipate additional energy to charge and discharge  $C_{PAR}$ . In other words,  $P_R$  is higher when  $C_{FLY}$  is on chip, which is why internal  $P_{R(INT)}$  is higher than external  $P_{R(EXT)}$  in Fig. 7. Switch drivers also consume power  $P_G$  when they charge and discharge gate capacitors  $C_{G.EQ}$  every cycle:

$$P_{\rm G} = 2 \left( 0.5 C_{\rm G.EQ} V_{\rm O}^2 \right) f_{\rm SW}.$$

(10)

Since increasing  $i_{PH}$  means  $f_{SW}$  increases,  $P_G$  also increases with  $P_{PV}$ . As with the SI counterpart, Fig. 7 also assumes quiescent controller power  $P_Q$  is constant across  $P_{PV}$  at 1  $\mu$ W.

Fig. 7. Simulated on-chip and off-chip switched-capacitor losses across  $P_{PV}$ .

## D. Inductor- versus Capacitor-Based Harvesters

Irrespective of the approach, RMS current increases with  $P_{PV}$ , so Ohmic losses P<sub>R</sub> are proportional to P<sub>PV</sub> and also dominant across most of PPV. PR is lower in SI converters, however, because for the same P<sub>PV</sub>, i<sub>L</sub>'s peak is lower than i<sub>CFLY</sub>'s in SC circuits, which means RMS currents are higher in SC implementations.  $P_R$  is also considerably higher when  $C_{FLY}$  is on chip, which means SC circuits trade efficiency for integration. More importantly, SI converters need only two transistors to boost  $v_{PV}$  to almost any output voltage  $V_{O}$ , whereas their SC counterparts require considerably more switches, and SC efficiencies tend to suffer when Vo varies [11]. This is important because the harvester's output is a battery voltage that spans, for example, 0.9 - 1.6 V for NiCd's and NiMH's, 2.7 – 4.2 V for Li Ions, and an even wider range for ultra capacitors. In other words, SI circuits that use only one in-package inductor seem better suited for harnessing light energy from miniaturized PV cells.

A more subtle, but equally important observation is that controller quiescent power  $P_Q$  consumes a considerable fraction of all the losses, where even though driving gates dissipate power  $P_G$ ,  $P_G$  is not as important. Note, however, these results only apply to chip-sized light-energy harvesters. Consider that, while voltage regulators draw whatever current is necessary from an input source to regulate the voltage across a variable load, light-energy harvesters regulate the voltage across an input source to draw and deposit as much current as possible into a low-impedance output: a battery. What is more, the power levels chip-sized PV cells generate are substantially low, at less than 100  $\mu$ W, so the conclusions drawn in [9], which relate to *higher voltage* and *higher power* voltage regulators, do not necessarily apply here.

### V. CONCLUSIONS

For chip-sized light-harvesting circuits to generate power, they must dissipate less energy than miniaturized photovoltaic (PV) cells generate, which might not even exceed 100 µW. The problem is that the photon-current conversion process, the parasitic diode  $(D_{PV})$  in the PV cell, and the harvester circuit all consume power. Therefore, to maximize PV power PPV and minimize D<sub>PV</sub> losses, the harvester should regulate PV voltage  $v_{PV}$  to optimum target  $V_{PV(OPT)}$  within a small window  $\Delta v_{PV(MAX)}$ . Similarly, to maximize harvested output power, the circuit should be efficient, which is to say it should transfer and condition power by switching an in-package inductor. Still, Ohmic losses  $P_R$  are dominant and proportional to  $P_{PV}$ , with controller quiescent power P<sub>Q</sub> not far behind and gatecharging losses P<sub>G</sub> further back. Interestingly, capacitor-based circuits consume more Ohmic power P<sub>R</sub> because they conduct higher RMS currents (since i<sub>CFLY</sub> peaks to a higher value than i<sub>L</sub>). Moreover, on-chip implementations lose additional power in charging and discharging parasitic bottom-plate capacitors. In other words, switched-inductor harvesters harness more light energy from chip-sized PV cells than switched-capacitor circuits, which is especially important when  $P_{PV}$  is low, cloud cover and artificial lighting conditions persist, and unobtrusiveness (i.e., integration) is imperative.

#### REFERENCES

- P. Dutta *et al.*, "Trio: enabling sustainable and scalable outdoor wireless sensor network deployments," *ISPN*, pp. 407-415, 2006.

- [2] G. Chen *et al.*,"Millimeter-scale nearly perpetual sensor system with stacked battery and solar cells," *Int. Solid-State Circuits Conference*, pp. 288-289, 2010.

- [3] E.O. Torres and G.A. Rincón-Mora, "Electrostatic Energy-Harvesting and Battery-Charging CMOS System Prototype," *IEEE Trans. on Circuits and Systems I*, vol.56, no.9, pp. 1938-1948, Sept. 2009.

- [4] E.O. Torres and G.A. Rincón-Mora "Long-lasting, self-sustaining, and energy-harvesting system-in-package (SiP) wireless micro-sensor solution", *Int. Conf. on Energy, Environment, and Disasters*, pp. 1-33, Jul. 2005.

- [5] A. Hande et al., "Indoor solar energy harvesting for sensor network router nodes," *Microprocessors & Microsystems*, vol. 31, no. 6, pp. 420-432, Sept. 2007.

- [6] T. Esram *et al.*, "Comparison of Photovoltaic Array Maximum Power Point Tracking Techniques," *IEEE Trans. on Energy Conversion*, vol. 22, no. 2, pp. 439-449, June 2007.

- [7] D. Brunelli *et al.*, "Design of a Solar-Harvesting Circuit for Batteryless Embedded Systems," *IEEE Trans. on Circuits and Systems I*, vol. 56, no. 11, pp. 2519-2528, Nov. 2009.

- [8] D. Baderna, "Efficiency comparison between doubler and Dickson charge pumps," *Int. Symp. on Circuits and Systems*, pp. 1891-1894, May 2005.

- [9] M.D. Seeman and S.R. Sanders, "Analysis and Optimization of Switched-Capacitor DC–DC Converters," *IEEE Trans. on Power Electronics*, vol. 23, no. 2, pp. 841-851, March 2008.

- [10] S. Kim and G.A. Rincon-Mora, "Achieving High Efficiency under Micro-Watt Loads with Switching Buck DC-DC Converters," *Journal* of Low-Power Electronics, vol. 5, no. 2, Aug. 2009.

- [11] I. Chowdhury and D. Ma, "Design of Reconfigurable and Robust Integrated SC Power Converter for Self-Powered Energy-Efficient

Devices," IEEE Trans. on Industrial Electronics, vol. 56, no. 10, pp. 4018-4028, Oct. 2009.