## Switched Inductors:

# **Building Blocks**

Ву

Gabriel Alfonso Rincón-Mora

School of Electrical and Computer Engineering Georgia Institute of Technology

Rincon-Mora.gatech.edu

Copyright © 2021 by G.A. Rincón-Mora

## Contents

|                                        | Page     |

|----------------------------------------|----------|

| List of Figures                        | v        |

| List of Abbreviations                  | vii      |

| 1. Current Sensors                     | 1        |

| 1.1. Series Resistance                 | 1        |

| A. Sense Resistor                      | 1        |

| B. MOS Resistance                      | 2        |

| C. Inductor Resistance                 | 3        |

| 1.2. Sense Transistor                  | 7        |

| A. Sense FET                           | 7        |

| B. Looped Sense FET                    | 9<br>10  |

| 1.3. Design Notes                      |          |

| 2. Voltage Sensors                     | 11       |

| 2.1. Voltage Divider                   | 11       |

| 2.2. Phase-Saving Voltage Divider      | 13       |

| 2.3. Voltage-Dividing Error Amplifier  | 14       |

| 3. Digital Blocks                      | 16       |

| 3.1. Push-Pull Logic                   | 16       |

| A. Inverter                            | 16       |

| B. NOR Gate                            | 18       |

| C. NAND Gate                           | 19       |

| D. Design Notes                        | 19       |

| 3.2. SR Flip Flops<br>3.3. Gate Driver | 20<br>21 |

| A. Minimum Delay                       | 21 22    |

| B. Gate-Charge Power                   | 22       |

| C. Shoot-Through Power                 | 25       |

| D. Design Notes                        | 27       |

| 3.4. Dead-Time Logic                   | 28       |

| 4. Comparator Blocks                   | 30       |

| 4.1. Comparators                       | 30       |

| 4.2. Hysteretic Comparators            | 30       |

| 4.3. Summing Comparators               | 31       |

| 5. Timing Blocks                       | 32       |

| 5.1. Clocked Sawtooth Generator        | 32       |

| 5.2. Sawtooth Oscillator               | 34       |

| 5.3. One-Shot Oscillator               | 36       |

| 6. Switch Blocks                | 37 |

|---------------------------------|----|

| 6.1. Class-A Inverters          | 37 |

| 6.2. Supply-Sensing Comparators | 39 |

| A. Low Side                     | 39 |

| B. High Side                    | 39 |

| C. Offset                       | 40 |

| D. Design Notes                 | 41 |

| 6.3. Zero-Current Detectors     | 42 |

| 6.4. Ring Suppressor            | 42 |

| 6.5. Switched Diodes            | 44 |

| A. Low Side                     | 44 |

| B. High Side                    | 45 |

| 6.6. Starter                    | 45 |

| A. Shutdown                     | 45 |

| B. Startup                      | 47 |

| 7. Summary                      | 47 |

### Switched Inductors: Building Blocks

Switched-inductor (SL) power supplies draw and deliver power. They are *regulators* when *feedback controllers* switch them so their outputs follow a target. *Voltage regulators* regulate voltage, *battery chargers* and *light-emitting diode* (LED) *drivers* regulate current, *battery-charging voltage regulators* regulate both, and *energy harvesters* regulate power.

Good power supplies are *efficient* and *accurate*. Efficient supplies lose a small fraction of the power they draw. And accurate supplies deliver the rest with a voltage or current that is very close to a target. Supplying power with a preset voltage or current like this is a form of *power conditioning*.

Power conditioning requires several actions. Some of these are analog in nature, others are digital, and those in between are mixed-mode. The building blocks that power supplies use reflect this diversity.

#### 1. Current Sensors

#### 1.1. Series Resistance

#### A. Sense Resistor

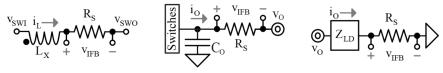

Inserting a *series resistor*  $R_s$  into the conduction path is one way of sensing current.  $R_s$  in Fig. 1 can be in series with the *switched inductor*  $L_x$ , the *output*  $v_0$ , or the *load*  $Z_{LD}$ . In all cases, the *current-feedback translation*  $\beta_{IFB}$  that senses  $v_0$ 's *output current*  $i_0$  or  $L_x$ 's *inductor current*  $i_L$  is  $R_s$ :

$$\beta_{\rm IFB} \equiv \frac{v_{\rm IFB}}{i_{\rm LO}} = \frac{i_{\rm LO}R_{\rm S}}{i_{\rm LO}} = R_{\rm S}.$$

(1)

Fig. 1. Sense resistor.

average  $v_{SW}$ 's and extract  $R_L$ 's dc voltage. A tuned bypass filter can extract  $R_L$ 's dc and ac voltages, but with a  $v_{IFB}$  that swings with one of the  $v_{SW}$ 's. This is not a problem for bucks and boosts because they only have one  $v_{SW}$ , which the filter can average. This filter can also amplify  $R_L$ 's ac voltage, but only after  $L_X$  overcomes  $R_L$  and  $C_F$  shorts.

$R_s$ ,  $R_{Ds}$ , and  $R_L$  all vary with temperature and fabrication runs. Sense FETs are less sensitive because they track the switches they sense. But since they are much smaller, mismatches offset their outputs. Their translations are also nonlinear. A feedback loop can fix this, but by slowing the response. Although not always, basic sense FETs often offer more favorable tradeoffs than looped FETs and series resistances. Table I summarizes some of these points.

|             | Series Resistances       |                       |                |                |                            | Sense FETs              |        |

|-------------|--------------------------|-----------------------|----------------|----------------|----------------------------|-------------------------|--------|

|             | Rs                       | Rs RDS Filtered RL    |                | Basic          | Looped                     |                         |        |

|             | K5                       | IXD5                  | Low Pass       | Tuned          | Untuned                    | Dasie                   | Loopeu |

| Input       | i <sub>O/L</sub>         | i <sub>O/L(E/D)</sub> | $i_{L(DC)}$    | i <sub>L</sub> | $i_{L\left(DC/AC\right)}$  | i <sub>O/L(E/D)</sub>   |        |

| Gain        | Rs                       | R <sub>DS</sub>       | $R_L$          | R <sub>L</sub> | $\frac{L_{X}}{R_{F}C_{F}}$ | $\frac{R_{IFB}}{A_{I}}$ |        |

| Power       | $P_R + P_Q$              | P <sub>Q</sub>        | P <sub>Q</sub> | P <sub>Q</sub> | P <sub>Q</sub>             | P <sub>Q</sub>          |        |

| Sensitivity | $T_J$ & Fabrication Runs |                       |                |                | Mismatch                   |                         |        |

| Sensitivity | $R_L \propto f_O$        |                       |                |                | Nonlinear                  | Linear                  |        |

Table I. Current Feedback Translations

#### 2. Voltage Sensors

#### 2.1. Voltage Divider

$v_O$  is typically over the *bandgap voltage*  $V_{BG}$  or sub- $V_{BG}$  that sets the *reference voltage*  $v_R$ . So in most cases, the *feedback translation*  $\beta_{FB}$  attenuates  $v_O$  to the *feedback voltage*  $v_{FB}$  that the *error amp*  $A_E$  compares to  $v_R$ . This is why  $v_R$  is normally 1.2 V or lower and  $\beta_{FB}$  is a fraction.

$$\Delta PM = \tan^{-1} \frac{f_{0dB}}{z_{FB}} - \tan^{-1} \frac{f_{0dB}}{p_{FB}}.$$

(22)

**Example 5**: Determine  $C_F$  and  $\Delta PM$  for Example 4 when  $f_{0dB}$  is 100 kHz. **Solution**:

$$R_{FB1} = 168 \text{ kG2 and } R_{FB2} = 232 \text{ kG2 from Example 4}$$

$$z_{FB} = \frac{1}{2\pi R_{FB1}C_F} = \frac{1}{2\pi (168 \text{ k})C_F} = \frac{950 \text{ n}}{C_F}$$

$$p_{FB} = \frac{1}{2\pi (R_{FB1} || R_{FB2})C_F} = \frac{1}{2\pi (168 \text{ k} || 232 \text{ k})C_F} = \frac{1.6 \mu}{C_F}$$

$$\frac{p_{FB}}{f_{0dB}} = \frac{1.6 \mu}{(100 \text{ k})C_F} = \frac{f_{0dB}}{z_{FB}} = \frac{(100 \text{ k})C_F}{950 \text{ n}}$$

$$\therefore C_F = 12 \text{ pF} \implies z_{FB} = 79 \text{ kHz} \text{ and } p_{FB} = 130 \text{ kHz}$$

$$\Delta PM = \tan^{-1} \frac{f_{0dB}}{z_{FB}} - \tan^{-1} \frac{f_{0dB}}{p_{FB}}$$

$$= \tan^{-1} \frac{100 \text{ k}}{79 \text{ k}} - \tan^{-1} \frac{100 \text{ k}}{130 \text{ k}} = 14^{\circ}$$

#### 2.3. Voltage-Dividing Error Amplifier

When the feedback loop includes  $A_E$ , integrating  $\beta_{FB}$  into  $A_E$ 's stabilizer can save power, components, and area. The *voltage-dividing error amplifier* in Fig. 11, for example, integrates the voltage divider into the feedback network of an *inverting op amp*.  $R_{FB1}$  and  $R_{FB2}$  translate  $v_O$  to  $v_{FB}$ and  $A_V$ ,  $Z_{F1}$ , and  $Z_{F2}$  with  $R_{FB1}$  set  $A_E$ 's gain and stabilizing response.

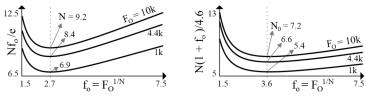

$Z_{F1}$  and  $Z_{F2}$  are typically capacitors  $C_{F1}$  and  $C_{F2}$  with, on occasion, series resistors  $R_{F1}$  and  $R_{F2}$ . This way,  $Z_{F1}$  and  $Z_{F2}$  open at low frequency. So  $\beta_{FB}$  translates  $v_O$  to  $v_{FB}$  with  $R_{FB1}$  and  $R_{FB2}$  and  $A_E$ 's *low-frequency gain*  $A_{E0}$  amplifies  $v_R$  and  $v_{FB}$ 's error with  $A_{V0}$ . self-loading ( $k_{SL}$ ) is negligible. N(1 + f<sub>o</sub>)/(1 + 3.6) when f<sub>o</sub> is 3.6 nears a more optimal N<sub>0</sub> because  $k_{SL}$  is more realistic near one.

Fig. 19. Optimal gate-driver setting for minimum delay.

$M_N$  in  $K_1$  pulls  $v_{O1}$  low when  $i_N$  overcomes  $i_P$ , after  $v_{GS}$  reaches  $v_T$ . As  $v_{GS}$  rises over  $v_T$  and  $v_{O1}$  falls across  $\Delta v_{O(MAX)}$ ,  $M_N$  enters and remains in triode.  $M_P$  is similarly in triode as  $v_{SG}$  climbs over  $v_T$  and  $v_O$  rises. When strengths match,  $R_{D1}$  is roughly  $M_N$ 's triode resistance when  $v_{GS}$  nears  $v_T$ :

$$R_{D1} \approx R_{N1} \Big|_{v_{DS} < v_{DS(SAT)}}^{v_{GS} > V_{TN0}} \approx \frac{L_{N1} - 2L_{OL}}{W_{N1}K_{N}'(v_{T} - V_{TN0})},$$

(33)

where  $L_{OL}$  is *overlap length*.  $C_{GI}$  is roughly the *channel capacitance*  $C_{CH1}$  that W's and L's set across the *oxide capacitance*  $C_{OX}$ " (per unit area):

$$C_{GI} \approx C_{CH1} = C_{CHN1} + C_{CHP1} \approx (W_{N1}L_{N1} + W_{P1}L_{P1})C_{OX}".$$

(34)

**Example 7**: Determine N and  $t_P$  with the inverter from Example 6 when  $L_{MIN}$  is 250 nm,  $L_{OL}$  is 30 nm,  $C_{OX}$ " is 6.9 fF/ $\mu$ m<sup>2</sup>, and the load is a 100-mm wide, 250-nm long NFET.

Solution:

$$\begin{split} W_{N1} &= 3 \ \mu m \ \text{and} \ W_{P1} &= 6.7 W_{N1} = 20 \ \mu m \ \text{from Example 6} \\ L_{N1} &\equiv L_{P1} \equiv L_{MIN} = 250 \ \text{nm} \\ C_{GI} &= C_{GN} + C_{GP} = C_{GN} + 6.7 C_{GN} = 7.7 C_{GN} \\ F_{O} &= \frac{C_{GO}}{C_{GI}} = \frac{W_{GO}}{7.7 W_{GN}} = \frac{100 \text{m}}{7.7 (3 \mu)} = 4.4 \text{k} \\ F_{O} &= f_{o}^{N_{0}} \equiv 3.6^{N_{0}} = 4.4 \text{k} \quad \therefore \ N \ge N_{0} = 6.6 \ \rightarrow \ N \equiv 7 \ \text{Stages} \end{split}$$

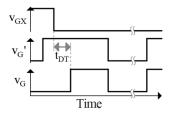

same time. Consider gate command  $v_G'$  and *gate voltages*  $v_G$  and  $v_{GX}$  in Fig. 21, for example.  $v_G$  rises a  $t_{DT}$  after adjacent  $v_{GX}$  falls, even when  $v_G'$  commands a high before  $v_{GX}$  falls.

Fig. 21. Dead-time response.

$t_{DT}$  only applies to closing events, when burning unnecessary power is possible. Opening switches is inherently safe because it stops current flow. This is why  $v_G$  falls with  $v_G'$  without delay in Fig. 21.

$t_{DT}$  should delay turn-on commands only when adjacent commands are high, when shorting events are possible. Whenever safe, reducing delays helps the system respond and recover more quickly. This is why v<sub>G</sub> in Fig. 21 rises with v<sub>G</sub>' without delay the second time v<sub>G</sub>' transitions high.

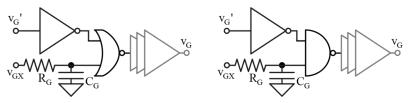

To assert these states, *dead-time circuits* should sense, delay, and compare neighboring commands with  $v_G$ '. R's and C's in Fig. 22, for example, sense and delay neighboring  $v_G$ 's. And NOR and NAND gates compare these delayed signals with  $v_G$ ' to determine  $v_G$ . R's and C's or inverter chains can sense and delay neighboring  $v_G$ 's.

Fig. 22. Active-high and -low dead-time circuits.

The NOR gate outputs an active-high command when  $v_G$ ' is high after neighboring  $v_G$ 's fall. The NAND gate outputs an active-low command Switched Inductors: Building Blocks

$$\mathbf{v}_{\mathrm{S(HI)}} = \mathbf{v}_{\mathrm{T}} + \left(\frac{\mathbf{I}_{\mathrm{S}}}{\mathbf{C}_{\mathrm{S}}}\right) \mathbf{t}_{\mathrm{P}}^{+} = \mathbf{v}_{\mathrm{T}} + \left(\frac{1.7\mu}{5p}\right) (100n) \equiv 300 \text{ mV}$$

$$\therefore \quad \mathbf{v}_{\mathrm{T}} = 270 \text{ mV}$$

#### 5.3. One-Shot Oscillator

*One-shot oscillators* are *pulse generators*. But more specifically, they are interruptible relaxation oscillators. They pulse once when pulsed and pulse continuously when kept enabled.

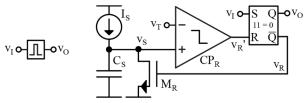

Like *ring oscillators*, they usually close inverting feedback loops that internal components delay. In the case of Fig. 29,  $CP_R$ , the flip flop, and  $M_R$  close the loop and  $I_S$  and  $C_S$  delay it.  $v_O$  pulses each time  $v_I$  pulse-sets the flip flop and oscillates between states when  $v_I$  stays high.

Fig. 29. One-shot oscillator.

Raising  $v_I$  sets  $v_O$  and opens  $M_R$  to start a pulse. I<sub>S</sub> charges  $C_S$  across the pulse until  $M_R$  resets  $v_S$ . The *pulse width*  $t_{PW}$  is the time  $C_S$ ,  $CP_R$ , and the reset-dominant flip flop need to ramp  $v_S$  to  $v_T$ , trip, and reset:

$$t_{PW} = \left(\frac{C_{S}}{I_{S}}\right) \left(v_{S(HI)} - v_{S(LO)}\right) = \left(\frac{C_{S}}{I_{S}}\right) \left(v_{T} - v_{S(LO)}\right) + t_{P}^{+} + t_{SR}^{+}.$$

(48)

So across this  $t_{PW}$ ,  $I_S$  charges  $C_S$  over  $v_T$  across  $t_P^+$  and  $t_{SR}^+$ :

$$v_{S(HI)} = v_T + \left(\frac{I_S}{C_S}\right) \left(t_P^+ + t_{SR}^+\right).$$

(49)

Keeping  $v_I$  high sets another pulse when the reset command  $v_R'$  falls. This happens after  $v_S$  falls below  $v_T$ . The time between pulses  $t_{OFF}$  is the

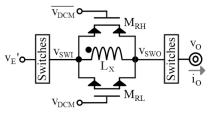

Fig. 34. Ring suppressor.

As  $R_L$  dampens oscillations,  $v_{SWI}$  and  $v_{SWO}$  approach one another until  $v_L$  is zero. Since bucks and boosts exclude input or output switches,  $v_{SW}$  approaches  $v_O$  in bucks and  $v_{IN}$  in boosts. The  $C_{SW}$  that sets the *LC time constant*  $\tau_{LC}$  in buck–boosts is the series combination of  $C_{SWI}$  and  $C_{SWO}$ .

These oscillations can last several cycles. This is unfortunate because the *electromagnetic interference* (EMI)  $i_L$  generates can alter the feedback action that sets  $v_O$  or  $i_O$ . The purpose of  $M_{RL/H}$  is to suppress this "ringing".

The *ring suppressor* is a resistor that the ZCD invokes when  $L_X$  enters DCM. This  $R_R$  should burn  $E_{LC}$  before  $L_X$  receives it. Since  $C_{SW}$  and  $L_X$  exchange  $E_{LC}$  every quarter *LC period*  $t_{LC}$ ,  $t_{RC}$  should be less than 25% $t_{LC}$ :

$$t_{s} = t_{RC} \approx 2.3\tau_{RC} = 2.3R_{R}C_{SW} < \frac{t_{LC}}{4} = \frac{2\pi\tau_{LC}}{4} = \frac{2\pi/4}{\sqrt{L_{X}C_{SW}}},$$

(54)

where suppression time  $t_s$  is roughly the  $t_{RC}$  needed to collapse 90% of  $v_L$ .

Low- and high-side switches can realize this  $R_R$ . A PFET  $M_{RH}$  may be sufficient when  $v_0$  is high and an NFET  $M_{RL}$  when  $v_{IN}$  exceeds  $v_0$  and  $v_0$ is low. Both may be necessary when  $v_{IN}$  is not much greater than a low  $v_0$ . Regardless, these FETs are often mostly in triode when they collapse  $v_L$ .

**Example 16**:Determine  $W_R$  when  $v_O$  for a buck is 1.8 V,  $L_X$  is 10  $\mu$ H,  $C_{SW}$  is 5 pF,  $W_{MIN}$  is 3  $\mu$ m,  $L_R$  is 250 nm,  $L_{OL}$  is 30 nm,  $K_P'$  is 40  $\mu$ A/V<sup>2</sup>, and  $V_{TP0}$  is -700 mV.

Solution:

$$L_{CH} = L_R - 2L_{OL} = 250n - 2(30n) = 190 \text{ nm}$$

efficient than adding resistance. This resistance, however, varies widely with temperature and fabrication runs. Sense transistors often offer more favorable tradeoffs in this respect. Their weakness is mismatch.

Voltage dividers sense and translate voltages well because resistors usually match well. Paralleling a capacitor across the top resistor is an easy way of inserting a phase-saving zero–pole pair. Combining the voltage divider with the stabilizing error amplifier is also possible.

Amplifiers and comparators compare analog inputs and output a digital output that indicates which is higher. Comparators are basically amplifiers without stabilizing features. Adding flip flops or positive feedback establishes hysteresis. And paralleling transconductors adds inputs so the output trips with the polarity of their sum.

*Constant-time loops* rely on timing blocks to operate. Capacitors are essential here. In sawtooth generators, current into a capacitor ramps a voltage that a flip flop resets. Sawtooth and one-shot oscillators ramp a voltage that a comparator resets. And a flip flop in the one shot can interrupt the oscillations to pulse once or any number of times.

Digital blocks control switching events. SR flip flops use digital gates and positive feedback to decouple on–off commands. Inverter chains with increasingly larger stages drive large power switches. And dead-time logic keeps adjacent power switches from shorting their inputs.

Switch blocks help manage switching events. Supply-sensing comparators are useful in this respect. They help zero-current detectors invoke DCM operation and switched diodes behave like ideal diodes. They can also trigger the ring suppressor, which subdues DCM oscillations.

The starter is also important. It keeps initial shutdown conditions from spiking i<sub>L</sub>. Current and duty-cycle limiters are useful guardrails during